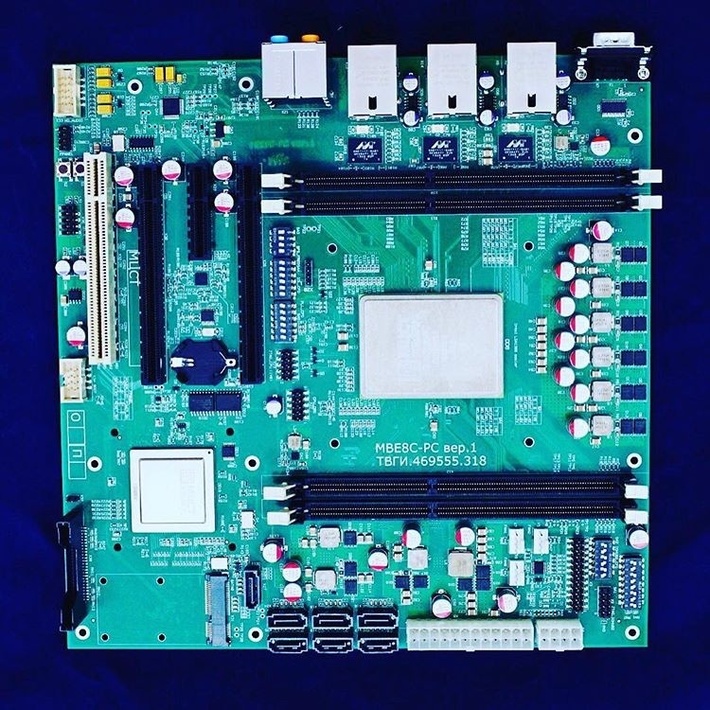

Эльбрус-8С: результаты теста SPEC CPU 2006

На стратегической сессии «РОССИЙСКИЕ АППАРАТНО-ПРОГРАММНЫЕ РЕШЕНИЯ» представитель МЦСТ Константин Трушкин представил результаты теста SPEC CPU 2006 для микропроцессора «Эльбрус-8С».

Источник: www.youtube.com

Другие публикации по теме

Поделись позитивом в своих соцсетях

02.07.1712:59:39

02.07.1716:26:49

02.07.1717:24:12

02.07.1717:31:45

26.10.1820:56:30

02.07.1718:46:31

03.07.1705:49:47

03.07.1715:45:52

03.07.1718:38:35

02.07.1722:59:41